-

解讀小器件、大作用,MOS管五大關鍵點

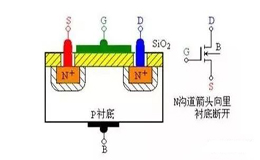

在一塊濃度較低的P型硅上擴散兩個濃度較高的N型區作為漏極和源極,半導體表面覆蓋二氧化硅絕緣層并引出一個電極作為柵極。

2018-05-25

MOS管 N溝道

-

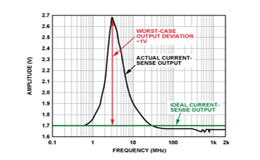

電磁干擾(EMI)濾波減少精密模擬應用中的誤差

在醫療設備、汽車儀器儀表和工業控制等科技領域中,當設備設計涉及應變計、傳感器接口和電流監控時,通常需要采用精密模擬前端放大器,以便提取并放大非常微弱的真實信號,并抑制共模電壓和噪聲等無用信號。首先,設計人員將集中精力確保器件級噪聲、失調、增益和溫度穩定性等精度參數符合應用要求。

2018-05-25

電磁干擾 濾波

-

Synopsys IC Validator獲得GLOBALFOUNDRIES 14LPP物理驗證Signoff認證

Synopsys 宣布,Synopsys IC Validator工具已獲得GLOBALFOUNDRIES(GF )認證,將用于GF 14LPP工藝技術的物理驗證Signoff。憑借此Signoff認證,設計工 程師可以借助IC Validator的快速性和可擴展性,實現高水平的可制造性和最大生產 量。目前GF可以提供各種認證的運行集,包括DRC、LVS和金...

2018-05-24

Synopsys IC 物理驗證 Signoff認證

-

高速電路設計中不可忽略的一個重要因素

在高速電路設計中,鏈路中的每一個參數都有可能導致傳遞的信號出問題。今天就和大家分享一個平常大家不太注意的參數。

2018-05-24

高速電路 信號完整性 電路設計

-

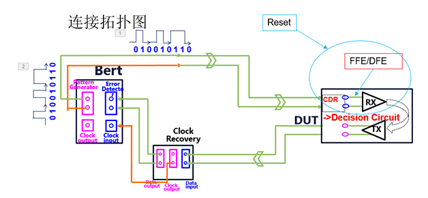

巧用Bertscope進行芯片/系統的接收端容限測試和調試分析

在用戶進行系統或者芯片測試的時候,一般主要驗證幾個方面的性能和可靠性,包括系統發送端的信號質量,鏈路的損耗/串擾,接收端的容限。如下圖1,一個鏈路系統的基本架構。通常在發送端會使用FFE來補償鏈路的損耗,接收端會采用DFE/FFE等方法來進行均衡,一些比較高速率的標準如PCIE 4.0/5.0,SAS4等...

2018-05-24

Bertscope BSX 芯片

-

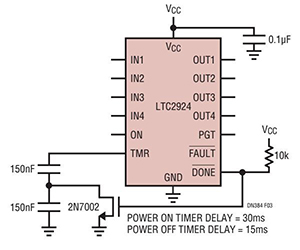

如何防止系統受損?從電源排序入手

諸如電信設備、存儲模塊、光學系統、網絡設備、服務器和基站等許多復雜系統都采用了 FPGA 和其他需要多個電壓軌的數字 IC,這些電壓軌必須以一個特定的順序進行啟動和停機操作,否則 IC 就會遭到損壞。

2018-05-24

電源排序 FPGA 電壓軌 數字IC

-

第三屆大聯大創新設計大賽晉級團隊出爐

大聯大控股宣布,第三屆“大聯大創新設計大賽”(WPG i-Design Contest)在經過專家評審后已有55支團隊從271支報名隊伍中脫穎而出。大聯大將為進入復賽的團隊提供從開發板到資金的支持,并將對最后獲獎的團隊提供價值不菲的獎金。

2018-05-23

大聯大大賽 創新設計

-

意法半導體推出專業MEMS開發工具,實現MEMS 傳感可視化

意法半導體推出可視化的 Profi MEMS Tool 開發平臺,方便工程師 查看MEMS 傳感器的工作狀態,加快產品上市時間,并最大限度提高新產品設計的性能。

2018-05-23

意法半導體 MEMS Profi-MEMS-Tool

-

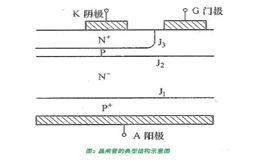

詳解晶閘管的基本結構知識

一般地,具有PNPN四層三結結構的器件是晶閘管。嚴格來說,根據國際電工委員會(IEC)的標準定義,具有3個或者3個以上PN結,其伏安特性至少在一個象限內具有導通和阻斷兩個穩定狀態,并可以在兩個狀態之間進行切換的電力半導體器件為晶閘管。晶閘管可以分為很多類型,比如內部存在反并聯二極管的逆導...

2018-05-23

晶閘管 半控型晶閘管

- 從失效案例逆推:獨石電容壽命計算與選型避坑指南

- 性能與成本的平衡:獨石電容原廠品牌深度對比

- 精密信號鏈技術解析:從原理到高精度系統設計

- 儀表放大器如何成為精密測量的幕后英雄?

- 儀表放大器如何驅動物聯網終端智能感知?

- 連偶科技攜“中國IP+AIGC+空間計算”三大黑科技首秀西部電博會!

- 優化儀表放大器的設計提升復雜電磁環境中的抗干擾能力

- 0.01%精度風暴!儀表放大器如何煉成工業自動化的“神經末梢”

- 0.1微伏決定生死!儀表放大器如何成為醫療設備的“聽診器”

- 國產技術出海新機遇!elexcon深圳展開啟全球觀眾登記通道

- 雙核驅動新質生產力:西部電博會聚焦四川雙萬億電子集群

- 高結溫IC設計避坑指南:5大核心挑戰與應對策略

- 車規與基于V2X的車輛協同主動避撞技術展望

- 數字隔離助力新能源汽車安全隔離的新挑戰

- 汽車模塊拋負載的解決方案

- 車用連接器的安全創新應用

- Melexis Actuators Business Unit

- Position / Current Sensors - Triaxis Hall