【導讀】在高速數字電路與高頻模擬系統主宰電子設計的今天,PCB疊層設計早已超越簡單的“線路承載”功能,成為決定產品性能、可靠性與成本的核心環節。合理的疊層結構如同摩天大樓的地基,為信號完整性(SI)、電源完整性(PI)和電磁兼容性(EMC)提供堅實保障;而失敗的疊層方案則可能引發信號畸變、電源噪聲、輻射超標等一系列棘手問題。本文將深入剖析PCB疊層設計的關鍵性,揭示常見設計“深坑”,并提供不同應用場景下的優選方案與實用避坑策略。

在高速數字電路與高頻模擬系統主宰電子設計的今天,PCB疊層設計早已超越簡單的“線路承載”功能,成為決定產品性能、可靠性與成本的核心環節。合理的疊層結構如同摩天大樓的地基,為信號完整性(SI)、電源完整性(PI)和電磁兼容性(EMC)提供堅實保障;而失敗的疊層方案則可能引發信號畸變、電源噪聲、輻射超標等一系列棘手問題。本文將深入剖析PCB疊層設計的關鍵性,揭示常見設計“深坑”,并提供不同應用場景下的優選方案與實用避坑策略。

一、 為什么PCB疊層設計如此關鍵?

PCB疊層設計絕非簡單的層數堆砌,其核心價值在于通過精密控制以下要素,滿足復雜電路的物理與電氣需求:

1. 信號完整性(SI)的守護者:

●可控阻抗: 高速信號(如DDR, PCIe, USB3+)要求精確的傳輸線阻抗(如50Ω, 90Ω差分)。疊層決定了信號層與參考平面(電源或地)的距離、介質厚度及材料特性(Dk值),直接影響特征阻抗計算與實現精度。阻抗失配會導致信號反射、過沖/下沖、時序抖動。

●減少串擾: 相鄰信號層或同層走線過近會引發電磁耦合(串擾)。合理的疊層通過增加層間距、在關鍵信號層間插入參考平面(屏蔽層)、采用正交走線策略等,有效隔離敏感信號。

●提供低損耗回路: 高頻信號的返回電流傾向于在參考平面上緊貼信號走線下方流動(最小回路電感)。疊層需確保每個信號層都有完整、鄰近的參考平面,為返回電流提供低阻抗路徑,減少電磁輻射和環路電感。

2. 電源完整性(PI)的基石:

●低阻抗電源分配網絡(PDN): 疊層通過設置專門的電源層(Power Plane)和地層(Ground Plane),并盡量靠近(形成平板電容),為芯片提供低阻抗、低感抗的電源通路。核心電壓(如Vcore)通常需要緊鄰地平面。

●去耦電容有效性: 疊層結構影響電源平面與地平面之間的固有電容以及去耦電容的安裝位置環路電感,決定高頻噪聲的濾波效果。不當的層間距或平面分割會削弱去耦效果。

3. 電磁兼容性(EMC)的屏障:

●屏蔽與抑制輻射: 完整的地平面和電源平面是最有效的屏蔽層。合理的疊層(如“地-信號-信號-地”的對稱結構)能將高速信號產生的電磁場約束在板內,減少向外的輻射(RE)。同時也能降低外部干擾(如ESD、射頻)對內層敏感電路的影響(抗擾度RI)。

●控制共模電流: 良好的參考平面設計有助于控制共模電流路徑,減少共模輻射。

4. 熱管理與結構可靠性:

●散熱路徑: 大功率器件產生的熱量可通過過孔(Thermal Via)傳導至內層平面或外層散熱銅箔。疊層設計需考慮這些熱通道的布局。

●抑制翹曲: 對稱的疊層結構(如芯板與PP半固化片材料、銅厚分布對稱)能有效平衡應力,減少PCB在制造和焊接過程中的翹曲變形風險。

5. 成本與制造可行性的平衡: 層數增加直接帶來成本上升。疊層設計需在滿足電氣性能的前提下,選擇最經濟的層數和材料組合。同時需考慮工廠的加工能力(如最小線寬/線距、層間對準精度、壓合能力)。

二、 PCB疊層結構基礎與關鍵要素

1. 核心組成部分:

●芯板(Core): 剛性基材(通常是FR-4玻璃纖維環氧樹脂),雙面覆銅。是疊層的骨架。

●半固化片(Prepreg, PP): 未完全固化的樹脂浸漬玻璃布。在壓合過程中熔化流動,填充空隙并粘合相鄰層。其樹脂含量影響最終介電常數(Dk)和厚度。

●銅箔(Copper Foil): 形成導線、焊盤和平面層。厚度常用盎司(oz)表示(1oz ≈ 35μm)。

●阻焊層(Solder Mask): 覆蓋在表層銅箔上,絕緣防護,開窗處露出焊盤。

●絲印層(Silkscreen): 標識元件位置、方向等信息。

2. 疊層描述關鍵參數:

●層序(Layer Stackup Sequence): 各層(信號層S、電源層P、地層G)的排列順序。是設計的核心。

●層厚(Thickness): 包括各層間介質(PP)厚度、芯板厚度、銅層厚度。決定阻抗和層間電容。

●介電常數(Dk, εr): 基材(芯板、PP)的電氣特性,影響信號傳播速度和阻抗計算。FR-4典型值約4.2-4.5(頻率不同有差異)。

●損耗角正切(Df, tanδ): 基材的損耗特性,影響信號衰減(插入損耗)。高頻高速應用需選擇低Df材料(如M7NE, Megtron 6)。

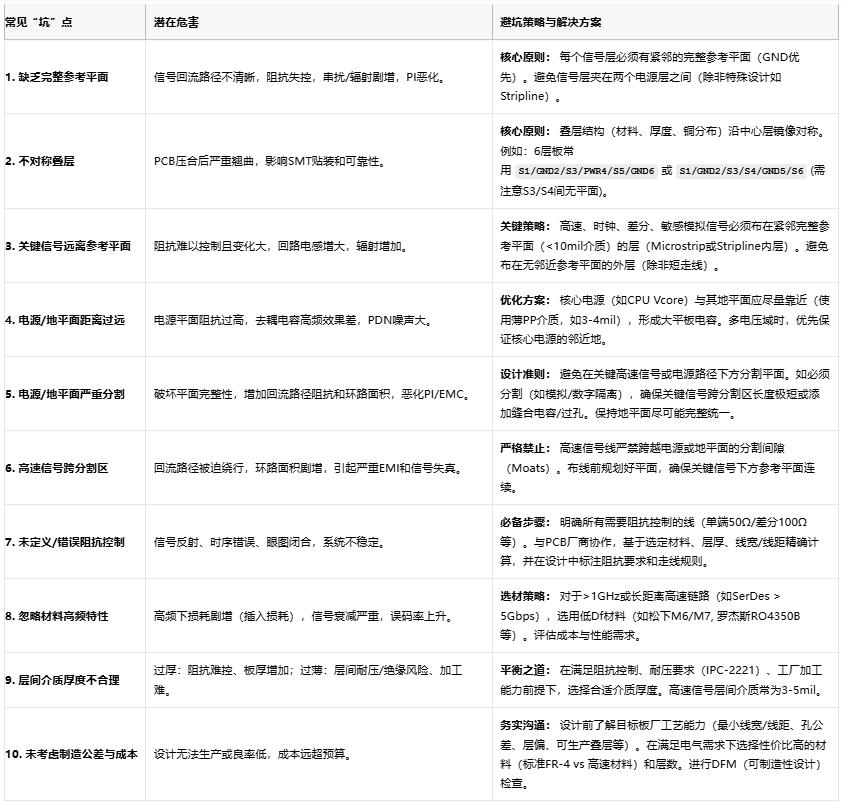

三、 PCB疊層設計避坑指南:十大常見“深坑”與對策

四、 不同應用場景的PCB疊層方案選擇(含典型示例)

結語:疊層設計 – 沒有最好,只有最合適

PCB疊層設計是一門融合電氣工程、材料科學和制造工藝的精密藝術。不存在一種“放之四海而皆準”的完美疊層模板。成功的核心在于深刻理解電路的核心需求(速度、功耗、信號類型、EMC等級、成本),并據此做出精準權衡:

● 成本敏感型項目:4層板通常是性價比最優解,牢記對稱疊層和參考平面完整性原則。

● 性能導向的高速系統:6層及以上是起點,優先選擇Stripline布線,確保關鍵電源鄰近完整地平面,必要時采用低損耗材料。

● 混合信號挑戰:物理隔離(獨立地平面)和單點接地是基石,層數需滿足隔離和布線需求。

● 微型化訴求:擁抱HDI技術,疊層設計需與微孔工藝緊密結合。

避坑的關鍵在于預見性: 在設計初期就投入精力進行疊層規劃,利用仿真工具(SI/PI/EMC)評估關鍵方案,并與可靠的PCB制造商緊密溝通其工藝能力和材料庫。記住,一個經過深思熟慮、量身定制的疊層方案,是避免后期昂貴返工、確保產品一次成功并滿足所有性能指標的“地基密碼”。它將無形的電氣規則轉化為有形的物理結構,最終鑄就穩定、可靠、高效的電子設備基石。

推薦閱讀:

選型不再糾結!一文讀懂力芯微、TI、ADI升壓轉換器核心差異

離座秒鎖屏!意法半導體新推人體存在檢測技術守護PC智能設備隱私安全